#### Description

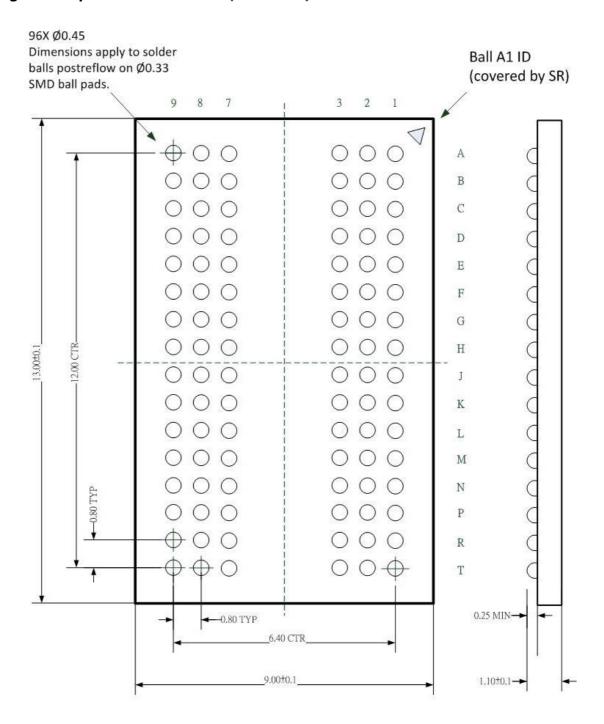

The EM47DM1688SBC is a 2Gb DDR3 SDRAM consisting of 16Mb x 8 banks x 16 bits I/O. The EM47DM1688SBC is packaged into 9x13 mm 96 Balls FBGA.

#### **Features**

- Power Supply:  $V_{DD} = 1.5V \pm 0.075V$

- $V_{DDQ} = 1.5V \pm 0.075V$

- Functionality and operations comply with the DDR3 SDRAM standards

- 8 internal banks

- 1 rank

- Speed: -125 is DDR3-1600

- Data transfer rates: PC3-12800

- Bi-Directional Differential Data Strobe

- 8 bit pre-fetch

- Burst Length (BL) switch on-the-fly BL8 or BC4 (Burst Chop)

- On-Die Termination (ODT)

- Programmable CAS (READ) latency (CL)

- Programmable posted CAS additive latency (AL)

- Programmable CAS (WRITE) latency (CWL)

- This product is in compliance with the RoHS directive

- Operating temperature: 0°C to +85°C

-64ms, 8192-cycle refresh at 0°C to +85°C

## **Revision History**

| Revision                 | Update        |

|--------------------------|---------------|

| Revision 1.0 (Aug. 2021) | First release |

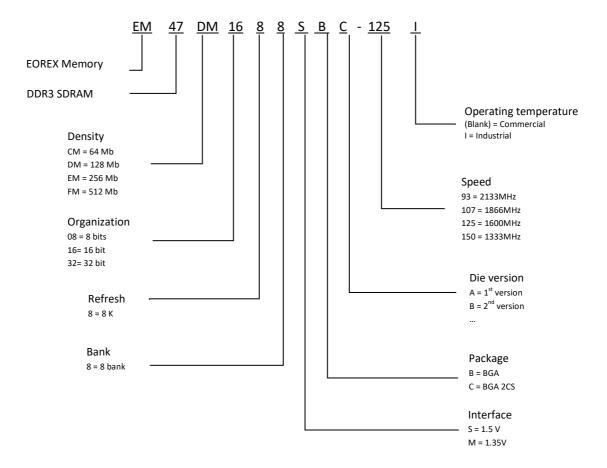

## **Part Numbering**

# **Ordering Information**

| Part No           | Organization | Voltage | Max. Frequency       | Package  | Grade      |

|-------------------|--------------|---------|----------------------|----------|------------|

| EM47DM1688SBC-125 | 128M x 16    | 1.5V    | DDR3-1600 (11-11-11) | FBGA-96B | Commercial |

Note: Speed (<sup>t</sup>CK\*) is in order of CL-<sup>t</sup>RCD-<sup>t</sup>RP

## **Ball Assignment**

|        | Top view |       |   |        |        |      |  |  |  |

|--------|----------|-------|---|--------|--------|------|--|--|--|

| 1      | 2        | 3     |   | 7      | 8      | 9    |  |  |  |

| VDDQ   | DQ13     | DQ15  | Α | DQ12   | VDDQ   | VSS  |  |  |  |

| VSSQ   | VDD      | VSS   | В | /UDQS  | DQ14   | VSSQ |  |  |  |

| VDDQ   | DQ11     | DQ9   | С | UDQS   | DQ10   | VDDQ |  |  |  |

| VSSQ   | VDDQ     | UDM   | D | DQ8    | VSSQ   | VDD  |  |  |  |

| VSS    | VSSQ     | DQ0   | Е | LDM    | VSSQ   | VDDQ |  |  |  |

| VDDQ   | DQ2      | LDQS  | F | DQ1    | DQ3    | VSSQ |  |  |  |

| VSSQ   | DQ6      | /LDQS | G | VDD    | VSS    | VSSQ |  |  |  |

| VREFDQ | VDDQ     | DQ4   | Н | DQ7    | DQ5    | VDDQ |  |  |  |

| NC     | VSS      | /RAS  | J | CK     | VSS    | NC   |  |  |  |

| ODT    | VDD      | /CAS  | K | /CK    | VDD    | CKE  |  |  |  |

| NC     | /CS      | /WE   | L | A10/AP | ZQ     | NC   |  |  |  |

| VSS    | BA0      | BA2   | М | NC     | VREFCA | VSS  |  |  |  |

| VDD    | А3       | A0    | N | A12/BC | BA1    | VDD  |  |  |  |

| VSS    | A5       | A2    | Р | A1     | A4     | VSS  |  |  |  |

| VDD    | A7       | A9    | R | A11    | A6     | VDD  |  |  |  |

| VSS    | /RESET   | A13   | Т | NC     | A8     | VSS  |  |  |  |

## **Ball Description**

| Symbol          | Туре  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ск, /ск         | Input | Clock: CK and /CK are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of /CK.  Output (read) data is referenced to the crossings of CK and /CK                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CKE             | Input | Clock Enable: CKE HIGH activates, and CKE Low deactivates, internal clock signals and device input buffers and output drivers. Taking CKE Low provides Pre-charge Power-Down and Self Refresh operation (all banks idle), or Active Power-Down (Row Active in any bank). CKE is asynchronous for self-refresh exit. After VREFCA has become stable during the power on and initialization sequence, it must be maintained during all operations (including Self-Refresh). CKE must be maintained high throughout read and write accesses. Input buffers, excluding CK, /CK, ODT and CKE are disabled during Power Down. Input buffers, excluding CKE, are disabled during Self Refresh. |

| /cs             | Input | <b>Chip Select:</b> All commands are masked when /CS is registered HIGH. /CS provides for external Rank selection on systems with multiple Ranks. /CS is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ODT             | Input | On Die Termination: ODT (registered HIGH) enables termination resistance internal to the DDR3 SDRAM. When enabled, ODT is only applied to each DQ, DQS, /DQS and DM. The ODT pin will be ignored if the Mode Register (MR1) is programmed to disable ODT.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| /RAS, /CAS, /WE | Input | Command Inputs: /RAS, /CAS and /WE (along with /CS) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| UDM, LDM        | Input | Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH coincident with that input data during a Write access. DM is sampled on both edges of DQS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BAO~ BA2        | Input | Bank Address Inputs: BAO-BA2 define the bank to which an Active, Read, Write or Pre-charge command is being applied. Bank address also determines if the mode register or extended mode register is to be accessed during a MRS cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A0~ A13         | Input | Address Inputs: Provide the row address for Active commands and the column address for Read/Write commands to select one location out of the memory array in the respective bank. The address inputs also provide the op-code during Mode Register Set commands. (A10/AP and A12/BC have additional functions, see below)                                                                                                                                                                                                                                                                                                                                                               |

| A10 / AP        | Input | Auto Pre-charge: A10 is sampled during Read/Write commands to determine whether Auto pre-charge should be performed to the accessed bank after the Read/Write operation (HIGH: Auto pre-charge; LOW: No Auto pre-charge). A10 is sampled during a Pre-charge command to determine whether the Pre-charge applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be pre-charged, the bank is selected by bank addresses.                                                                                                                                                                                                                                          |

| A12 / BC        | Input | <b>Burst Chop:</b> A12 is sampled during Read and Write commands to determine if burst chop (on-the-fly) will be performed. (HIGH: no burst chop, LOW: burst chopped). See command truth table for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Symbol                     | Туре                | Function                                                                                                                                                                                                                                                   |

|----------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /RESET                     | Input               | Input Reset: /RESET is an active LOW CMOS input referenced to VSS. The /RESET input receiver is a CMOS input defined as a rail-to-rail signal with DC HIGH $\geq$ 0.8 × VDD and DC LOW $\leq$ 0.2 × VDDQ. /RESET assertion and desertion are asynchronous. |

| DQ0~ DQ15                  | 1/0                 | Data Input/ Output: Bi-directional data bus.                                                                                                                                                                                                               |

| UDQS, /UDQS<br>LDQS, /LDQS | 1/0                 | <b>Data Strobe:</b> Output with read data, input with write data. Edge-aligned with read data, centered in write data. DDR3 SDRAM supports differential data strobe only and does not support single-ended.                                                |

| V <sub>DDQ</sub>           | Supply              | DQ Power Supply: 1.5V +/- 0.075V                                                                                                                                                                                                                           |

| Vssq                       | Supply              | DQ Ground                                                                                                                                                                                                                                                  |

| $V_{DD}$                   | Supply              | Power Supply: 1.5V +/- 0.075V                                                                                                                                                                                                                              |

| V <sub>SS</sub>            | Supply              | Ground                                                                                                                                                                                                                                                     |

| VREFDQ                     | Reference           | Reference voltage for DQ Pins                                                                                                                                                                                                                              |

| VREFCA                     | Reference           | Reference voltage for Command, Control, and Address Pins                                                                                                                                                                                                   |

| ZQ                         | Reference           | Reference Pin for ZQ calibration: series 240Ω resistor to VSS                                                                                                                                                                                              |

| NC                         | -                   | Not Connected Internally.                                                                                                                                                                                                                                  |

| Note: Input only pins (I   | BA0-BA2, A0-A14, /R | AS, /CAS, /WE, /CS, CKE, ODT and /RESET) do not supply termination.                                                                                                                                                                                        |

#### **Absolute Maximum Rating**

| Symbol    | Item                          | Rating                       |        | Units         |  |   |

|-----------|-------------------------------|------------------------------|--------|---------------|--|---|

| VIN, VOUT | Input, Output Voltage         | -0.4 ~ +1.975                |        | -0.4 ~ +1.975 |  | V |

| VDD       | Power Supply Voltage          | -0.4 ~ +1.975                |        | -0.4 ~ +1.975 |  | V |

| VDDQ      | Power Supply Voltage          | -0.4 ~ +1.975                |        | V             |  |   |

| ТОР       | Operating Temperature Range   | Commercial                   | 0~ +85 | °C            |  |   |

| TSTG      | Storage Temperature Range     | 0~+                          | 95     | °C            |  |   |

| VREFCA    | Reference Voltage for Control | -0.4 ~ 0.6 × V <sub>DD</sub> |        | V             |  |   |

| VREFDQ    | Reference Voltage for DQ      | -0.4 ~ 0.6                   | × VDDQ | V             |  |   |

Note: Caution Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification.

## **Recommended DC Operating Conditions**

$(VDD, VDDQ = 1.5V \pm 0.075)$

| Symbol             | Parameter & Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                   | -125      | Units |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|

| IDD <sub>1</sub>   | Operating One Bank Active-Read-Pre-charge Current:  CKE: High; External clock: On; t <sub>CK</sub> , nRC, nRAS, nRCD, CL: see timing used table; BL: 81;  AL: 0; /CS: High between ACT, RD and PRE; Command, Address, Data IO: partially toggling; DM: stable at 0; Bank Activity: Cycling with one bank active at a time;  Output Buffer and RTT: Enabled in Mode Registers; ODT Signal: stable at 0                                                         | Max<br>45 | mA    |

| IDD <sub>2P1</sub> | Pre-charge Power-Down Current Fast Exit:  CKE: Low; External clock: On; t <sub>CK</sub> , CL: see timing used table; BL: 8; AL: 0;/CS: stable at 1; Command, Address: stable at 0; Data IO: FLOATING; DM: stable at 0; Bank Activity: all banks closed; Output Buffer and RTT: Enabled in Mode Registers; ODT Signal: stable at 0; Pre-charge Power Down Mode: Fast Exit                                                                                      | 11        | mA    |

| IDD <sub>2N</sub>  | Pre-charge Standby Current:  CKE: High; External clock: On; t <sub>CK</sub> , CL: see timing used table; BL: 8; AL: 0;/CS: stable at 1; Command, Address: partially toggling; Data IO: FLOATING; DM: stable at 0; Bank Activity: all banks closed; Output Buffer and RTT: Enabled in Mode Registers; ODT                                                                                                                                                      | 15        | mA    |

| IDD <sub>3P</sub>  | Active Power-Down Current:  CKE: Low; External clock: On; t <sub>CK</sub> , CL: see timing used table; BL: 8; AL: 0;/CS: stable at 1; Command, Address: stable at 0; Data IO: FLOATING; DM: stable at 0; Bank Activity: all banks open; Output Buffer and RTT: Enabled in Mode Registers; ODT Signal: stable                                                                                                                                                  | 16        | mA    |

| IDD <sub>4W</sub>  | Operating Burst Write Current:  CKE: High; External clock: On; t <sub>CK</sub> , CL: see timing used table; BL: 8; AL: 0;/CS: High between WR; Command, Address: partially toggling; Data IO: seamless write data burst with different data between one burst and the next one; DM: stable at 0; Bank Activity: all banks open, WR commands cycling through banks: 0,0,1,1,2,2,; Output Buffer and RTT: Enabled in Mode Registers; ODT Signal: stable at HIGH | 105       | mA    |

# EM47DM1688SBC

| Symbol            | Parameter & Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -125 | Units |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| IDD <sub>5B</sub> | Burst Refresh Current:  CKE: High; External clock: On; t <sub>CK</sub> , CL, nRFC: see timing used table; BL: 8; AL: 0; /CS:  High between REF; Command, Address: partially toggling; Data IO: FLOATING; DM: stable at 0; Bank Activity: REF command every nRFC; Output Buffer and RTT: Enabled in Mode Registers; ODT Signal: stable at 0                                                                                                                                                                        | 130  | mA    |

| IDD <sub>6</sub>  | Self-Refresh Current: Normal Temperature Range; TC: 0- 85°C; Auto Self-Refresh (ASR): Disabled; Self-Refresh Temperature Range (SRT): Normal; CKE: Low; External clock: Off; CK and /CK: LOW; CL: see timing used table; BL: 8; AL: 0; CS, Command, Address, Data IO: FLOATING; DM: stable at 0; Bank Activity: Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers; ODT Signal: FLOATING                                                                                                    | 12   | mA    |

| IDD <sub>7</sub>  | Operating Bank Interleave Read Current; CKE: High; External clock: On; $t_{\text{CK}}$ , nRC, nRAS, nRCD, nRRD, nFAW, CL: see timing used table; BL: 8; AL: CL-1; CS: High between ACT and RDA; Command, Address: partially toggling; Data IO: read data bursts with different data between one burst and the next one; DM: stable at 0; Bank Activity: two times interleaved cycling through banks (0, 1,7) with different addressing; Output Buffer and RTT: Enabled in Mode Registers; ODT Signal: stable at 0 | 140  | mA    |

- Note 1: Burst Length: BL8 fixed by MRS: set MR0 A[1,0]=00B

- Note 2: Output Buffer Enable: set MR1 A[12] = 0B; set MR1 A[5, 1] = 01B; RTT\_Nom enable: set MR1 A[9, 6, 2] = 011B; RTT\_Wr enable: set MR2 A[10, 9] = 10B

- Note 3: Pre-charge Power Down Mode: set MR0 A12 = 0B for Slow Exit or MR0 A12 = 1B for Fast Exit

- Note 4: Auto Self-Refresh (ASR): set MR2 A6 = 0B to disable or 1B to enable feature

- Note 5: Self-Refresh Temperature Range (SRT): set MR2 A7 = 0B for normal or 1B for extended temperature range

- Note 6: Refer to DRAM supplier data sheet and/or SPD to determine if optional features or requirements are supported by DDR3 SDRAM

- Note 7: Read Burst type: Nibble Sequential, set MRO A[3] = 0B

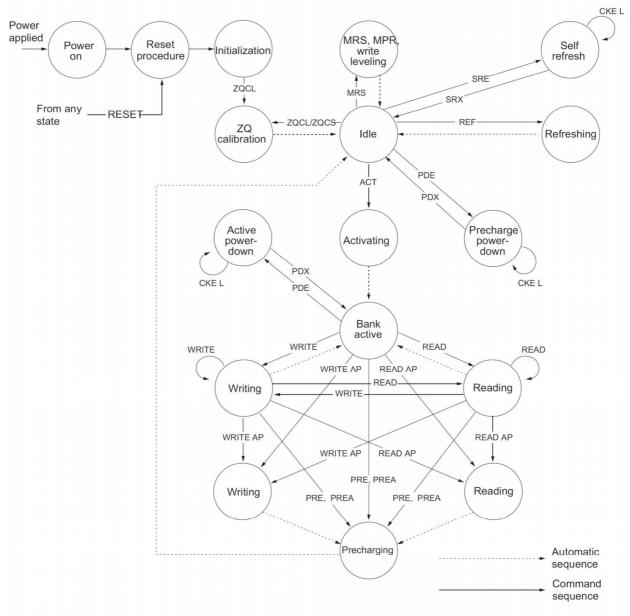

### Simplified State Diagram

ACT = ACTIVATE

MPR = Multipurpose register

MRS = Mode register set

PDE = Power-down entry

PDX = Power-down exit

PRE = PRECHARGE

PREA = PRECHARGE ALL

READ = RD, RDS4, RDS8

READ AP = RDAP, RDAPS4, RDAPS8

REF = REFRESH

RESET = START RESET PROCEDURE

SRE = Self refresh entry

SRX = Self refresh exit

WRITE = WR, WRS4, WRS8

WRITE AP = WRAP, WRAPS4, WRAPS8 ZQCL = ZQ LONG CALIBRATION

ZQCS = ZQ SHORT CALIBRATION

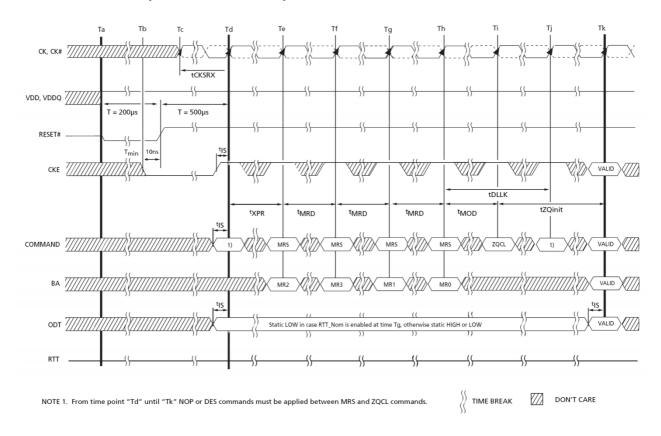

#### Reset and Power up Initialization Sequence

## **Mode Register Setting**

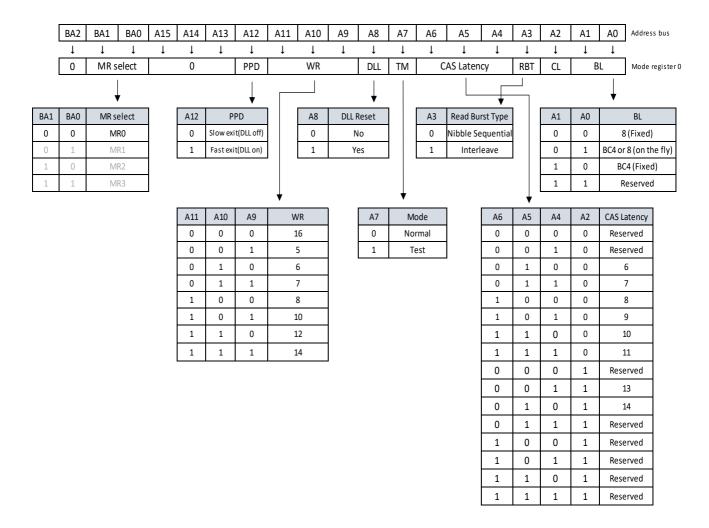

#### Mode Register 0 (MR0)

The base register, mode register 0 (MR0), is used to define various DDR3 SDRAM modes of operation. These definitions include the selection of a burst length, burst type, CAS latency, operating mode, DLL RESET, write recovery, and pre-charge power-down mode.

#### **Burst Length**

Burst length is defined by MR0[1:0]. Read and write accesses to the DDR3 SDRAM are burst-oriented, with the burst length being programmable to 4 (chop) mode, 8 (fixed) mode, or selectable using A12 during a READ/WRITE command (on-the-fly). The burst length determines the maximum number of column locations that can be accessed for a given READ or WRITE command. When MR0[1:0] is set to 01 during a READ/WRITE command, if A12 = 0, then BC4 mode is selected. If A12 = 1, then BL8 mode is selected. Specific timing diagrams, and turnaround between READ/WRITE, are shown in the READ/WRITE sections of this document.

When a READ or WRITE command is issued, a block of columns equal to the burst length is effectively selected. All accesses for that burst take place within this block, meaning that the burst will wrap within the block if a boundary is reached. The block is uniquely selected by A[i:2] when the burst length is set to 4 and by A[i:3] when the burst length is set to 8, where Ai is the most significant column address bit for a given configuration. The remaining (least significant) address bit(s) is (are) used to select the starting location within the block. The programmed burst length applies to both READ and WRITE bursts.

## Mode Register 0 (MR0) Definitions

#### Note:

1. MR0[18, 15:13, 7] are reserved for future use and must be programmed to 0

#### **Burst Type**

Accesses within a given burst can be programmed to either a sequential or an interleaved order. The burst type is selected via MR0[3]. The ordering of accesses within a burst is determined by the burst length, the burst type, and the starting column address. DDR3 only supports 4-bit burst chop and 8-bit burst access modes. Full interleave address ordering is supported for READs, while WRITEs are restricted to nibble (BC4) or word (BL8) boundaries.

#### **Burst Order**

| Burst<br>Length | READ/<br>WRITE | Starting Column Address (A[2, 1, 0]) | Burst Type = Sequential<br>(Decimal) | Burst Type = Interleaved<br>(Decimal) | Notes    |

|-----------------|----------------|--------------------------------------|--------------------------------------|---------------------------------------|----------|

| 4(chop)         | READ           | 000                                  | 0, 1, 2, 3, Z, Z, Z, Z               | 0, 1, 2, 3, Z, Z, Z, Z                | 1, 2     |

|                 |                | 001                                  | 1, 2, 3, 0, Z, Z, Z, Z               | 1, 0, 3, 2, Z, Z, Z, Z                | 1, 2     |

|                 |                | 010                                  | 2, 3, 0, 1, Z, Z, Z, Z               | 2, 3, 0, 1, Z, Z, Z, Z                | 1, 2     |

|                 |                | 011                                  | 3, 0, 1, 2, Z, Z, Z, Z               | 3, 2, 1, 0, Z, Z, Z, Z                | 1, 2     |

|                 |                | 100                                  | 4, 5, 6, 7, Z, Z, Z, Z               | 4, 5, 6, 7, Z, Z, Z, Z                | 1, 2     |

|                 |                | 101                                  | 5, 6, 7, 4, Z, Z, Z, Z               | 5, 4, 7, 6, Z, Z, Z, Z                | 1, 2     |

|                 |                | 110                                  | 6, 7, 4, 5, Z, Z, Z, Z               | 6, 7, 4, 5, Z, Z, Z, Z                | 1, 2     |

|                 |                | 111                                  | 7, 4, 5, 6, Z, Z, Z, Z               | 7, 4, 5, 6, Z, Z, Z, Z                | 1, 2     |

|                 | WRITE          | 0 V V                                | 0, 1, 2, 3, X, X, X, X               | 0, 1, 2, 3, X, X, X, X                | 1, 3, 4  |

|                 |                | 1 V V                                | 4, 5, 6, 7, X, X, X, X               | 4, 5, 6, 7, X, X, X, X                | 1, 3, 4, |

| 8               | READ           | 000                                  | 0, 1, 2, 3, 4, 5, 6, 7               | 0, 1, 2, 3, 4, 5, 6, 7                | 1        |

| (fixed)         |                | 001                                  | 1, 2, 3, 0, 5, 6, 7, 4               | 1, 0, 3, 2, 5, 4, 7, 6                | 1        |

|                 |                | 010                                  | 2, 3, 0, 1, 6, 7, 4, 5               | 2, 3, 0, 1, 6, 7, 4, 5                | 1        |

|                 |                | 011                                  | 3, 0, 1, 2, 7, 4, 5, 6               | 3, 2, 1, 0, 7, 6, 5, 4                | 1        |

|                 |                | 100                                  | 4, 5, 6, 7, 0, 1, 2, 3               | 4, 5, 6, 7, 0, 1, 2, 3                | 1        |

|                 |                | 101                                  | 5, 6, 7, 4, 1, 2, 3, 0               | 5, 4, 7, 6, 1, 0, 3, 2                | 1        |

|                 |                | 110                                  | 6, 7, 4, 5, 2, 3, 0, 1               | 6, 7, 4, 5, 2, 3, 0, 1                | 1        |

|                 |                | 111                                  | 7, 4, 5, 6, 3, 0, 1, 2               | 7, 6, 5, 4, 3, 2, 1, 0                | 1        |

|                 | WRITE          | VVV                                  | 0, 1, 2, 3, 4, 5, 6, 7               | 0, 1, 2, 3, 4, 5, 6, 7                | 1, 3     |

#### Notes:

- 1. Internal READ and WRITE operations start at the same point in time for BC4 as they do for BL8.

- 2. Z = Data and strobe output drivers are in tristate.

- 3. V = A valid logic level (0 or 1), but the respective input buffer ignores level-on input pins.

- 4. X = "Don't Care."

#### **DLL Reset**

DLL RESET is defined by MR0[8]. Programming MR0[8] to 1 activates the DLL RESET function. MR0[8] is self-clearing, meaning it returns to a value of 0 after the DLL RESET function has been initiated.

Anytime the DLL RESET function is initiated, CKE must be HIGH and the clock held stable for 256 (tDLLK) clock cycles before a READ command can be issued. This is to allow time for the internal clock to be synchronized with the external clock. Failing to wait for synchronization can result in invalid output timing specifications, such as tDQSCK timings.

#### Write Recovery

WRITE recovery time is defined by MRO[11:9]. Write recovery values of 5, 6, 7, 8, 10, or 12 can be used by programming MRO[11:9]. The user is required to program the correct value of write recovery, which is calculated by dividing tWR (ns) by tCK (ns) and rounding up a non-integer value to the next integer: WR (cycles) = roundup (tWR (ns)/tCK (ns)).

## Pre-charge Power-Down (Pre-charge PD)

The pre-charge power-down (pre-charge PD) bit applies only when pre-charge power-down mode is being used. When MR0[12] is set to 0, the DLL is off during pre-charge power-down, providing a lower standby current mode; however, tXPDLL must be satisfied when exiting. When MR0[12] is set to 1, the DLL continues to run during pre-charge power-down mode to enable a faster exit of pre-charge power-down mode; however, tXP must be satisfied when exiting.

#### CAS Latency (CL)

CAS latency (CL) is defined by MR0[6:4]. CAS latency is the delay, in clock cycles, between the internal READ command and the availability of the first bit of output data. CL can be set to 5 through 14. DDR3 SDRAM do not support half-clock latencies.

If an internal READ command is registered at clock edge n, and the CAS latency is m clocks, the data will be available nominally coincident with clock edge n + m. See Speed Bin Tables for the CLs supported at various operating frequencies.

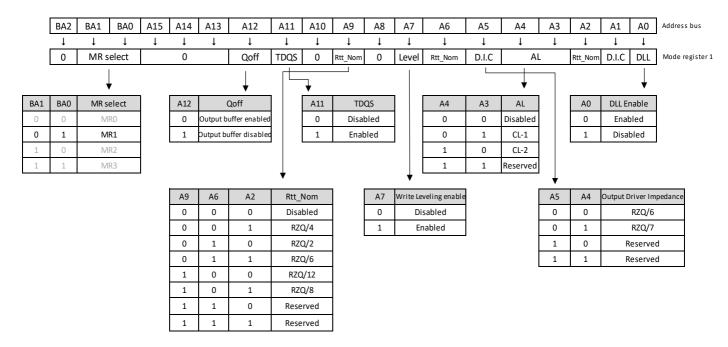

#### Mode Register 1 (MR1)

The mode register 1 (MR1) controls additional functions and features not available in the other mode registers: Q OFF (OUTPUT DISABLE), TDQS (for the x8 configuration only), DLL ENABLE/DLL DISABLE, RTT,nom value (ODT), WRITE LEVELING, POSTED.

CAS ADDITIVE latency, and OUTPUT DRIVE STRENGTH. These functions are controlled via the bits. The MR1 register is programmed via the MRS command and retains the stored information until it is reprogrammed, until /RESET goes LOW, or until the device loses power. Reprogramming the MR1 register will not alter the contents of the memory array, provided it is performed correctly.

The MR1 register must be loaded when all banks are idle and no bursts are in progress. The controller must satisfy the specified timing parameters tMRD and tMOD before initiating a subsequent operation.

#### Mode Register 1 (MR1) Definition

#### Notes:

- 1. MR1[18, 15:13, 10, 8] are reserved for future use and must be programmed to 0.

- 2. During write leveling, if MR1[7] and MR1[12] are 1, then all RTT,nom values are available for use.

- 3. During write leveling, if MR1[7] is a 1, but MR1[12] is a 0, then only RTT, nom write values are available for use.

#### **DLL Enable/ DLL Disable**

The DLL may be enabled or disabled by programming MR1[0] during the LOAD MODE command. The DLL must be enabled for normal operation. DLL enable is required during power-up initialization and upon returning to normal operation after having disabled the DLL for the purpose of debugging or evaluation. Enabling the DLL should always be followed by resetting the DLL using the appropriate LOAD MODE command.

If the DLL is enabled prior to entering self refresh mode, the DLL is automatically disabled when entering SELF REFRESH operation and is automatically re-enabled and reset upon exit of SELF REFRESH operation. If the DLL is disabled prior to entering self refresh mode, the DLL remains disabled even upon exit of SELF REFRESH operation until it is re-enabled and reset.

The DRAM is not tested to check normal mode timings or functionality when the DLL is disabled. An attempt has been made to have the DRAM operate in the normal mode where reasonably possible when the DLL has been disabled; however, by industry standard, a few known exceptions are defined:

- ODT is not allowed to be used

- The output data is no longer edge-aligned to the clock

- CL and CWL can only be six clocks

When the DLL is disabled, timing and functionality can vary from the normal operation specifications when the DLL is enabled. Disabling the DLL also implies the need to change the clock frequency.

#### **Output Drive Strength**

The DDR3 SDRAM uses a programmable impedance output buffer. The drive strength mode register setting is defined by MR1[5, 1]. RZQ/7 ( $34\Omega$  [NOM]) is the primary output driver impedance setting for DDR3 SDRAM devices. To calibrate the output driver impedance, an external precision resistor (RZQ) is connected between the ZQ ball and VSSQ. The value of the resistor must be  $240\Omega \pm 1\%$ .

The output impedance is set during initialization. Additional impedance calibration updates do not affect device operation, and all data sheet timings and current specifications are met during an update. To meet the  $34\Omega$  specification, the output drive strength must be set to  $34\Omega$  during initialization. To obtain a calibrated output driver impedance after power-up, the DDR3 SDRAM needs a calibration command that is part of the initialization and reset procedure.

## Output Enable/ Disable

The OUTPUT ENABLE function is defined by MR1[12]. When enabled (MR1[12] = 0), all outputs (DQ, DQS, /DQS) function when in the normal mode of operation. When disabled (MR1[12] = 1), all DDR3 SDRAM outputs (DQ and DQS, /DQS) are tri-stated. The output disable feature is intended to be used during IDD characterization of the READ current and during tDQSS margining (write leveling) only.

#### TDQS Enable

Termination data strobe (TDQS) is a feature of the x8 DDR3 SDRAM configuration that provides termination resistance (RTT) and may be useful in some system configurations. TDQS is not supported in x4 or x16 configurations. When enabled via the mode register (MR1[11]), the RTT that is applied to DQS and /DQS is also applied to TDQS and /TDQS. In contrast to the RDQS function of DDR2 SDRAM, DDR3's TDQS provides the termination resistance RTT only. The OUTPUT DATA STROBE function of RDQS is not provided by TDQS; thus, RON does not apply to TDQS and /TDQS. The TDQS and DM functions share the same ball. When the TDQS function is enabled via the mode register, the DM function is not supported. When the TDQS function is disabled, the DM function is provided, and the /TDQS ball is not used. The TDQS function is available in the x8 DDR3 SDRAM configuration only and must be disabled via the mode register for the x4 and x16 configurations.

#### **On-Die Termination**

ODT resistance RTT,nom is defined by MR1[9, 6, 2]. The RTT termination value applies to the DQ, DM, DQS, /DQS, and TDQS, /TDQS balls. DDR3 supports multiple RTT termination values based on RZQ/n where n can be 2, 4, 6, 8, or 12 and RZQ is  $240\Omega$ .

Unlike DDR2, DDR3 ODT must be turned off prior to reading data out and must remain off during a READ burst. RTT,nom termination is allowed any time after the DRAM is initialized, calibrated, and not performing read access, or when it is not in self refresh mode. Additionally, write accesses with dynamic ODT (RTT(WR)) enabled temporarily replaces RTT,nom with RTT(WR).

The actual effective termination, RTT(EFF), may be different from the RTT targeted due to nonlinearity of the termination. For RTT(EFF) values and calculations (see On-Die Termination (ODT). The ODT feature is designed to improve signal integrity of the memory channel by enabling the DDR3 SDRAM controller to independently turn on/off ODT for any or all devices. The ODT input control pin is used to determine when RTT is turned on (ODTL on) and off (ODTL off), assuming ODT has been enabled via MR1[9, 6, 2]. Timings for ODT are detailed in On-Die Termination (ODT).

#### Write Leveling

The WRITE LEVELING function is enabled by MR1[7]. Write leveling is used (during initialization) to deskew the DQS strobe to clock offset as a result of fly-by topology designs. For better signal integrity, The EM47DM1688SBC adopted fly-by topology for the commands, addresses, control signals, and clocks. The fly-by topology benefits from a reduced number of stubs and their lengths. However, fly-by topology induces flight time skews between the clock and DQS strobe (and DQ) at each DRAM DQ byte on the EM47DM1688SBC. Controllers will have a difficult time maintaining tDQSS, tDSS, and tDSH specifications without supporting write leveling in systems which use fly-by topology.

#### Posted CAS Additive Latency

POSTED CAS ADDITIVE latency (AL) is supported to make the command and data bus efficient for sustainable bandwidths in DDR3 SDRAM. MR1[4, 3] define the value of AL. MR1[4, 3] enable the user to program the DDR3 SDRAM with AL = 0, CL - 1, or CL - 2.

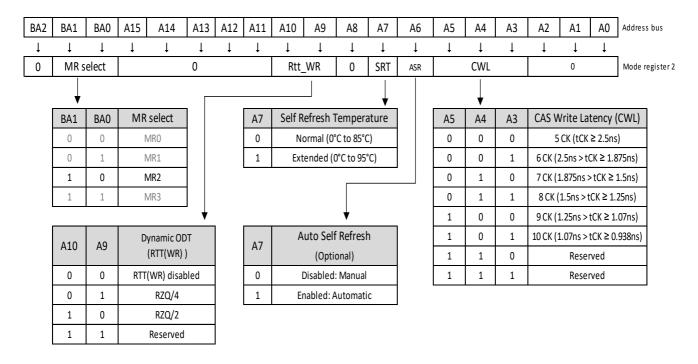

## Mode Register 2 (MR2)

The mode register 2 (MR2) controls additional functions and features not available in the other mode registers. These additional functions are CAS WRITE latency (CWL), AUTO SELF REFRESH (ASR), SELF REFRESH TEMPERATURE (SRT), and DYNAMIC ODT (RTT(WR)). The MR2 is programmed via the MRS command and will retain the stored information until it is programmed again or until the device loses power. Reprogramming the MR2 register will not alter the contents of the memory array, provided it is performed correctly. The MR2 register must be loaded when all banks are idle and no data bursts are in progress, and the controller must wait the specified time tMRD and tMOD before initiating a subsequent operation.

## Mode Register 2 (MR2) Definition

#### Note:

1. MR2[18, 15:11, 8, and 2:0] are reserved for future use and must all be programmed to 0.

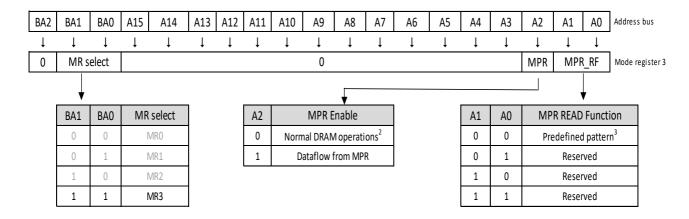

## Mode Register 3 (MR3)

The mode register 3 (MR3) controls additional functions and features not available in the other mode registers. Currently defined is the MULTIPURPOSE REGISTER (MPR). This function is controlled via the bits. The MR3 is programmed via the LOAD MODE command and retains the stored information until it is programmed again or until the device loses power. Reprogramming the MR3 register will not alter the contents of the memory array, provided it is performed correctly. The MR3 register must be loaded when all banks are idle and no data bursts are in progress, and the controller must wait the specified time tMRD and tMOD before initiating a subsequent operation.

#### Mode Register 3 (MR3) Definition

#### Notes:

- 1. MR3[18 and 15:3] are reserved for future use and must all be programmed to 0.

- 2. When MPR control is set for normal DRAM operation, MR3[1, 0] will be ignored.

- 3. Intended to be used for READ synchronization.

#### Multi Purpose Register (MPR)

The Multi Purpose Register (MPR) function is used to Read out a predefined system timing calibration bit sequence. To enable the MPR, a MODE Register Set (MRS) command must be issued to MR3 Register with bit A2 = 1. Prior to issuing the MRS command, all banks must be in the idle state (all banks pre-charged and tRP met). Once the MPR is enabled, any subsequent RD or RDA commands will be redirected to the Multi Purpose Register. When the MPR is enabled, only RD or RDA commands are allowed until a subsequent MRS command is issued with the MPR disabled (MR3 bit A2 = 0). Power-down mode, self-refresh and any other non-RD/RDA command is not allowed during MPR enable mode. The RESET function is supported during MPR enable mode.

## DDR3-1600MHz Speed Bins

| Speed Bin                                |                    |                      | DDR3-1600 |                       |                                                             |

|------------------------------------------|--------------------|----------------------|-----------|-----------------------|-------------------------------------------------------------|

| CL-t <sub>RCD</sub> -t <sub>RP</sub>     |                    |                      | 11-11-11  |                       |                                                             |

| Parameter                                |                    | Symbol               | Min       | Max                   | Unit                                                        |

| Internal read command to first data      |                    | <sup>t</sup> AA      | 13.75     | -                     | ns                                                          |

| ACT to internal read or write delay time |                    | <sup>t</sup> RCD     | 13.75     | -                     | ns                                                          |

| PRE command period                       | period             | <sup>t</sup> RP      | 13.75     | -                     | ns                                                          |

| ACT to ACT or                            | REF command period | <sup>t</sup> RC      | 48.75     | -                     | ns                                                          |

| ACT to PRE cor                           | nmand period       | <sup>t</sup> RAS     | 35        | 9 x <sup>t</sup> REFI | ns                                                          |

| Cl. F                                    | CWL=5              | <sup>t</sup> CK(AVG) | 3.0       | 3.3                   | ns                                                          |

| CL=5                                     | CWL=6, 7, 8        | <sup>t</sup> CK(AVG) | Reserved  | Reserved              | ns                                                          |

|                                          | CWL=5              | <sup>t</sup> CK(AVG) | 2.5       | 3.3                   | ns                                                          |

| CL=6                                     | CWL=6              | <sup>t</sup> CK(AVG) | Reserved  | Reserved              | ns                                                          |

|                                          | CWL=7, 8           | <sup>t</sup> CK(AVG) | Reserved  | Reserved              | ns                                                          |

|                                          | CWL=5              | <sup>t</sup> CK(AVG) | Reserved  | Reserved              | ns                                                          |

| Cl. 7                                    | CWL=6              | <sup>t</sup> CK(AVG) | 1.875     | <2.5                  | ns                                                          |

| CL=7                                     | CWL=7              | <sup>t</sup> CK(AVG) | Reserved  | Reserved              | ns                                                          |

|                                          | CWL=8              | <sup>t</sup> CK(AVG) | Reserved  | Reserved              | served ns served ns served ns served ns served ns served ns |

|                                          | CWL=5              | <sup>t</sup> CK(AVG) | Reserved  | Reserved              | ns                                                          |

| Cl. O                                    | CWL=6              | <sup>t</sup> CK(AVG) | 1.875     | <2.5                  | ns                                                          |

| CL=8                                     | CWL=7              | <sup>t</sup> CK(AVG) | Reserved  | Reserved              | ns                                                          |

|                                          | CWL=8              | <sup>t</sup> CK(AVG) | Reserved  | Reserved              | ns                                                          |

|                                          | CWL=5, 6           | <sup>t</sup> CK(AVG) | Reserved  | Reserved              | ns                                                          |

| CL=9                                     | CWL=7              | <sup>t</sup> CK(AVG) | 1.5       | <1.875                | ns                                                          |

|                                          | CWL=8              | <sup>t</sup> CK(AVG) | Reserved  | Reserved              | ns                                                          |

|                                          | CWL=5, 6           | <sup>t</sup> CK(AVG) | Reserved  | Reserved              | ns                                                          |

| CL=10                                    | CWL=7              | <sup>t</sup> CK(AVG) | 1.5       | <1.875                | ns                                                          |

|                                          | CWL=8              | <sup>t</sup> CK(AVG) | Reserved  | Reserved              | ns                                                          |

| CL 11                                    | CWL=5, 6, 7        | <sup>t</sup> CK(AVG) | Reserved  | Reserved              | ns                                                          |

| CL=11                                    | CWL=8              | <sup>t</sup> CK(AVG) | 1.25      | <1.5                  | ns                                                          |

| Supported CL S                           | Settings           | •                    | 5,6,7,8,  | 9,10,11               | nCK                                                         |

| Supported CW                             | L Settings         |                      | 5,6,      | 7,8                   | nCK                                                         |

# **Electrical Characteristics and AC Operating Conditions -1**

| Param                                 |                                  | Symbol                    | DDR                                                                                                                     | 3-1600 | Unit                                  | Notes  |

|---------------------------------------|----------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------|--------|

| Palali                                | leter                            | Syllibol                  | Min                                                                                                                     | Max    | Oilit                                 |        |

|                                       |                                  | C                         | Clock Timing                                                                                                            |        |                                       |        |

|                                       | T <sub>C</sub> = -55°C to 85°C   |                           | 8                                                                                                                       | 7800   | ns                                    | 9, 42  |

| Clock period average:                 | T <sub>C</sub> = >85°C to 95°C   | <sup>t</sup> CK (DLL_DIS) | 8                                                                                                                       | 3900   | ns                                    | 42     |

| DLL disable mode                      | T <sub>C</sub> = >95°C to 105°C  | CK (DLL_DIS)              | 8                                                                                                                       | 3900   | ns                                    | 42     |

|                                       | T <sub>C</sub> = >105°C to 125°C |                           | 8                                                                                                                       | 3900   | ns                                    | 42     |

| Clock period average: DLL enable mode |                                  | <sup>t</sup> CK (AVG)     | See Speed Bin Tables for <sup>t</sup> CK range allowed                                                                  |        | ns                                    | 10, 11 |

| High pulse width average              |                                  | <sup>t</sup> CH (AVG)     | 0.47                                                                                                                    | 0.53   | СК                                    | 12     |

| Low pulse width avera                 | ge                               | <sup>t</sup> CL (AVG)     | 0.47                                                                                                                    | 0.53   | СК                                    | 12     |

| Clash pariod iittan                   | DLL locked                       | <sup>t</sup> JITper       | -70                                                                                                                     | 70     | ps                                    | 13     |

| Clock period jitter                   | DLLlocking                       | <sup>t</sup> JITper,lck   | -60                                                                                                                     | 60     |                                       | 13     |

| Clock absolute period                 | Clock absolute period            |                           | MIN = <sup>t</sup> CK (AVG) MIN + <sup>t</sup> JITper MIN;<br>MAX = <sup>t</sup> CK (AVG) MAX + <sup>t</sup> JITper MAX |        | ps                                    |        |

| Clock absolute high pulse width       |                                  | <sup>t</sup> CH (ABS)     | 0.43                                                                                                                    | -      | <sup>t</sup> CK (AVG)                 | 14     |

| Clock absolute low pulse width        |                                  | <sup>t</sup> CL (ABS)     | 0.43                                                                                                                    | _      | <sup>t</sup> CK (AVG)                 | 15     |

| Coole to evel a like a                | DLL locked                       | <sup>t</sup> JITcc        |                                                                                                                         | 140    | ps                                    | 16     |

| Cycle-to-cycle jitter                 | DLLlocking                       | <sup>t</sup> JITcc,lck    |                                                                                                                         | 120    | ns ns ns ns cK CK ps ps ps  tCK (AVG) | 16     |

| _                                                                                                                                                                                                                    |                                |                               | DDR3                                                                                                                                                                                                   | -1600 |                                          |        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------|--------|

| Par                                                                                                                                                                                                                  | ameter                         | Symbol                        | Min                                                                                                                                                                                                    | Max   | Unit                                     | Notes  |

|                                                                                                                                                                                                                      | 2 cycles                       | <sup>t</sup> ERR2per          | -103                                                                                                                                                                                                   | 103   | ps                                       | 17     |

|                                                                                                                                                                                                                      | 3 cycles                       | <sup>t</sup> ERR3per          | -122                                                                                                                                                                                                   | 122   | ps                                       | 17     |

|                                                                                                                                                                                                                      | 4 cycles                       | <sup>t</sup> ERR4per          | -136                                                                                                                                                                                                   | 136   | ps                                       | 17     |

| Cumulative error across  Data setup time to DQS, /DQS  Data setup time to DQS, /DQS  Data hold time from DQS, /DQS  Minimum data pulse wi  DQS, /DQS to DQ skew, pe DQ output hold time fro DQ Low-Z time from CK, / | 5 cycles                       | <sup>t</sup> ERR5per          | -147                                                                                                                                                                                                   | 147   | ps                                       | 17     |

|                                                                                                                                                                                                                      | 6 cycles                       | <sup>t</sup> ERR6per          | -155                                                                                                                                                                                                   | 155   | ps                                       | 17     |

|                                                                                                                                                                                                                      | 7 cycles                       | <sup>t</sup> ERR7per          | -163                                                                                                                                                                                                   | 163   | ps                                       | 17     |

| Cumulative error across                                                                                                                                                                                              | 8 cycles                       | <sup>t</sup> ERR8per          | -169                                                                                                                                                                                                   | 169   | ps                                       | 17     |

|                                                                                                                                                                                                                      | 9 cycles                       | <sup>t</sup> ERR9per          | -175                                                                                                                                                                                                   | 175   | ps                                       | 17     |

|                                                                                                                                                                                                                      | 10 cycles                      | <sup>t</sup> ERR10per         | -180                                                                                                                                                                                                   | 180   | ps                                       | 17     |

|                                                                                                                                                                                                                      | 11 cycles                      | <sup>t</sup> ERR11per         | -184                                                                                                                                                                                                   | 184   | ps                                       | 17     |

|                                                                                                                                                                                                                      | 12 cycles                      | <sup>t</sup> ERR12per         | -188                                                                                                                                                                                                   | 188   | ps                                       | 17     |

|                                                                                                                                                                                                                      | <i>n</i> = 13, 14 49, 50cycles | <sup>t</sup> ERR <i>n</i> per |                                                                                                                                                                                                        |       | ps                                       | 17     |

|                                                                                                                                                                                                                      |                                | DQ Input Ti                   | iming                                                                                                                                                                                                  |       |                                          |        |

| ·                                                                                                                                                                                                                    | Base (specification)           | †DC (AC1F0)                   | 10                                                                                                                                                                                                     | _     | ps                                       | 18, 19 |

| DQS,/DQS                                                                                                                                                                                                             | V <sub>REF</sub> @ 1 V/ns      | <sup>t</sup> DS (AC150)       | 160                                                                                                                                                                                                    | -     | ps p | 19, 20 |

| Data setup time to                                                                                                                                                                                                   | Base (specification)           | tDC (AC13E)                   | -                                                                                                                                                                                                      | 1     | ps p | 18, 19 |

| DQS,/DQS                                                                                                                                                                                                             | V <sub>REF</sub> @ 1 V/ns      | <sup>t</sup> DS (AC135)       | -                                                                                                                                                                                                      | 1     | ps                                       | 19, 20 |

| Data hold time from                                                                                                                                                                                                  | Base (specification)           | tDH (DC100)                   | -147 147 ps -155 155 ps -163 163 ps -169 169 ps -175 175 ps -180 180 ps -184 184 ps -188 188 ps  terraper MIN = (1 + 0.68ln[n]) x till per MIN terraper MAX = (1 + 0.68ln[n]) x till per MAX  ning  10 | ps    | 18, 19                                   |        |

| DQS,/DQS                                                                                                                                                                                                             | V <sub>REF</sub> @ 1 V/ns      | DH (DC100)                    | 145                                                                                                                                                                                                    | ı     | ps p | 19, 20 |

| Minimum data pulse wi                                                                                                                                                                                                | dth                            | <sup>t</sup> DIPW             | 360                                                                                                                                                                                                    | ı     | ps                                       | 41     |

|                                                                                                                                                                                                                      |                                | DQ Output 1                   | Timing                                                                                                                                                                                                 |       |                                          |        |

| DQS, /DQS to DQ skew, per                                                                                                                                                                                            | raccess                        | <sup>t</sup> DQSQ             | -                                                                                                                                                                                                      | 100   | ps                                       |        |

| DQ output hold time from                                                                                                                                                                                             | n DQS, /DQS                    | <sup>t</sup> QH               | 0.38                                                                                                                                                                                                   | _     | <sup>t</sup> CK (AVG)                    | 21     |

| DQ Low-Z time from CK, /                                                                                                                                                                                             | СК                             | <sup>t</sup> LZDQ             | <del>-450</del>                                                                                                                                                                                        | 225   | ps                                       | 22, 23 |

| DQ High-Z time from CK,                                                                                                                                                                                              | DQ High-Z time from CK, /CK    |                               | -                                                                                                                                                                                                      | 225   | ps                                       | 22, 23 |

|                                                                                                                                                                                                                      | DC                             | Q Strobe Inpu                 | t Timing                                                                                                                                                                                               |       |                                          |        |

| DQS, /DQS rising to CK, /C                                                                                                                                                                                           | K rising                       | <sup>t</sup> DQSS             | -0.27                                                                                                                                                                                                  | 0.27  | СК                                       | 25     |

| DQS, /DQS differential in                                                                                                                                                                                            | nput low pulse width           | <sup>t</sup> DQSL             | 0.45                                                                                                                                                                                                   | 0.55  | СК                                       |        |

| Parameter                                     |                                       | symbol                          | DDR3-1600                                 |         |      |               |

|-----------------------------------------------|---------------------------------------|---------------------------------|-------------------------------------------|---------|------|---------------|

|                                               |                                       |                                 | Min                                       | Max     | Unit | Notes         |

| DQS, /DQS differential input high pulse width |                                       | <sup>t</sup> DQSH               | 0.45                                      | 0.55    | СК   |               |

| DQS, /DQS falling se                          | tup to CK, /CK rising                 | <sup>t</sup> DSS                | 0.18                                      | 1       | CK   | 25            |

| DQS, /DQS falling ho                          | old from CK, /CK rising               | <sup>t</sup> DSH                | 0.18                                      | 1       | СК   | 25            |

| DQS,/DQS different                            | ial WRITE preamble                    | <sup>t</sup> WPRE               | 0.9                                       | 1       | СК   |               |

| DQS, /DQS different                           | ial WRITE postamble                   | <sup>t</sup> WPST               | 0.3                                       | 1       | СК   |               |

|                                               |                                       | DQ St                           | trobe Output Timing                       |         |      |               |

| DQS, /DQS rising to,                          | from rising CK, /CK                   | <sup>t</sup> DQSCK              | -225                                      | 225     | ps   | 23            |

| DQS, /DQS rising when DLL is disable          | to/from rising CK, /CK<br>d           | <sup>t</sup> DQSCK<br>(DLL_DIS) | 1                                         | 10      | ns   | 26            |

| DQS, /DQS differer                            | itial output high time                | <sup>t</sup> QSH                | 0.40                                      | -       | CK   | 21            |

| DQS, /DQS differer                            | itial output low time                 | <sup>t</sup> QSL                | 0.40                                      | 1       | CK   | 21            |

| DQS, /DQS Low-Z ti                            | me (RL - 1)                           | <sup>t</sup> LZDQS              | -450                                      | 225     | ps   | 22, 23        |

| DQS, /DQS High-Z ti                           | me (RL + BL/2)                        | <sup>t</sup> HZDQS              | -                                         | 225     | ps   | 22, 23        |

| DQS, /DQS differen                            | tial READ preamble                    | <sup>t</sup> RPRE               | 0.9                                       | Note 24 | СК   | 23, 24        |

| DQS, /DQS differen                            | DQS, /DQS differential READ postamble |                                 | 0.3                                       | Note 27 | CK   | 23, 27        |

|                                               |                                       | Comma                           | nd and Address Timing                     |         |      |               |

| DLL locking time                              |                                       | <sup>t</sup> DLLK               | 512                                       | -       | CK   | 28            |

| CTRL, CMD, ADDR                               | Base (specification)                  | <sup>t</sup> IS (AC175)         | 45                                        | -       | ps   | 29,<br>30,44  |

| setuptoCK,/CK                                 | V <sub>REF</sub> @ 1 V/ns             |                                 | 220                                       | -       | ps   | 20, 30        |

| CTRL, CMD, ADDR                               | Base (specification)                  | <sup>t</sup> IS (AC150)         | 170                                       | -       | ps   | 29, 30,<br>44 |

| setuptoCK,/CK                                 | V <sub>REF</sub> @ 1 V/ns             |                                 | 320                                       | -       | ps   | 20, 30        |

| CTRL, CMD, ADDR                               | Base (specification)                  | <sup>t</sup> IS (AC135)         | _                                         | -       | ps   | 29, 30,<br>44 |

| setuptoCK, /CK                                | V <sub>REF</sub> @ 1 V/ns             |                                 | -                                         | -       | ps   | 20, 30        |

| CTRL, CMD, ADDR                               | Base (specification)                  | <sup>t</sup> IS (AC125)         | -                                         | 1       | ps   | 29,<br>30,44  |

| setuptoCK, /CK                                | V <sub>REF</sub> @ 1 V/ns             | (, 10110)                       | -                                         | -       | ps   | 20, 30        |

| CTRL, CMD, ADDR                               | Base (specification)                  | tIH (DC100)                     | 120                                       | -       | ps   | 29, 30        |

| hold from CK, /CK                             | V <sub>REF</sub> @ 1 V/ns             |                                 | 220                                       | -       | ps   | 20, 30        |

| Minimum CTRL, CMD, ADDR pulse width           |                                       | <sup>t</sup> IPW                | 560                                       | -       | ps   | 41            |

| ACTIVATE to internal READ or WRITE delay      |                                       | <sup>t</sup> RCD                | See Speed Bin Tables for <sup>t</sup> RCD |         | ns   | 31            |

| PRE-CHARGE command period                     |                                       | <sup>t</sup> RP                 | See Speed Bin Tables for <sup>t</sup> RP  |         | ns   | 31            |

| ACTIVATE-to-PRE-CHARGE command period         |                                       | <sup>t</sup> RAS                | See Speed Bin Tables for <sup>t</sup> RAS |         | ns   | 31, 32        |

| ACTIVATE-to-ACTIVATE command period           |                                       | <sup>t</sup> RC                 | See Speed Bin Tables for <sup>t</sup> RC  |         | ns   | 31, 43        |

| Parameter                                                                                |                                        | Symbol                                                     | DDR3-1600                                       |                 | 11   |              |

|------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------|-------------------------------------------------|-----------------|------|--------------|

|                                                                                          |                                        |                                                            | Min                                             | Max             | Unit | Notes        |

| ACTIVATE-to-ACTIVATE Minimum                                                             | x4/x8<br>(1KB page size)               | <sup>t</sup> RRD                                           | MIN = greater of 4CK or 6ns                     |                 | СК   | 31           |

| command period                                                                           | x16(2KB page size)                     | KIND                                                       | MIN = greater of 4CK or 7.5ns                   |                 |      |              |